International Journal of Computer Science and Information Technology Research ISSN 2348-120X (online) Vol. 3, Issue 3, pp: (155-157), Month: July - September 2015, Available at: www.researchpublish.com

# **Active Network Service Quality Improvement Using Cisco Quantum Flow Processor**

# S. Karthikeyan

Saveetha School Of Engineering, Chennai, India

Abstract: The quality of the network services can be improved by using the network processors. The network processor's will replace the normal network nodes into a active network nodes .so, that the quality of the networking services will be much higher compared to the normal networking modes. the replacement of the nodes are taken place in the form of the packets .by, replacing the normal nodes into the active nodes .the media files such as the photos, videos and other files which are to be accessed through networking can be processed quickly and efficiently. the processor for which the improvement of the network services called cisco quantum flow processor can be implemented to the hardware and software architectures so, that it will be executed efficiently Goal of improving networking service: the goal of the network capability services is to provide the better quality of service to the various selected networks, including the primary goal and asynchronus transmission mode (ATM).

Keywords: Active network nodes, the hardware and software architectures.

# 1. INTRODUCTION

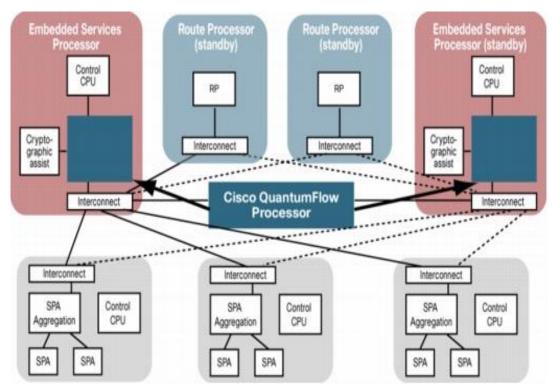

The Cisco Processor has been designed by Cisco as both a hardware and software architecture. The first generation resides on silicon with two pieces later generations may be single-chip solutions that adhere to the same software architecture described herein. The term "Cisco Processor" alone refers to the overall hardware and software architecture of the network processor

The cisco is the first generation 90 nm technology and converges into three possible applications:

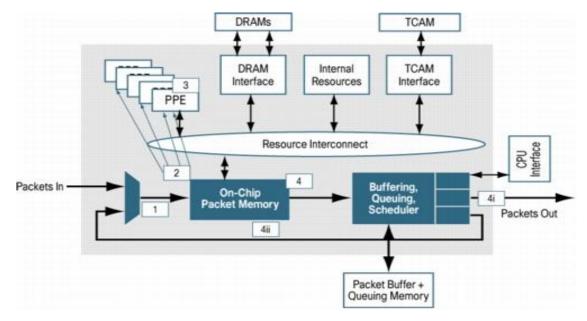

• It consolidates 40cores of the customized processor 900MHZ to 1.2GHZ. The requirements for external service blades inside the router reduced by the massive amount of parallel processing. All processing is performed on the chip

A dramatic offload of buffer, queue, and scheduling processing to address very complex subscriber- and interface-level queuing requirements of both enterprise and carrier networks today

And finally, the Cisco Quantum Flow Processor uses a software architecture based on a full ANSI-C development environment implemented in a true parallel processing environment. The other traditional network processor depends upon difficult-to-implement microcode, making it difficult and time-consuming to add new capabilities. Other network processors offer higher-level language development but into a feature pipelined architecture.in this cisco quantum processor we can use to increment the versions as per the customer requirements and languages built upon a powerful parallel processing architecture.

# 2. SCALE

The Cisco processor strikes the right balance between fast network processing and for virtually any current network service requirement. This processor enhance this advanced feature set with hundreds of customized network-processor resources, each capable of flexible flow processing for many applications into more than one lakh queues anywhere in the network.

International Journal of Computer Science and Information Technology Research ISSN 2348-120X (online)

Vol. 3, Issue 3, pp: (155-157), Month: July - September 2015, Available at: www.researchpublish.com

# 3. PERFORMANCE

The range 5 to 100 Gbps of packet-processing bandwidth by the cisco processor inside the chip, meaning that the entire payload and headers of frames are available for packet processing -- accelerating Deep Packet Inspection and application-specific processing.

The Cisco Processor is a massively parallel CPU architecture while incorporating a software architecture that allows fast delivery of data-path features and services. The processor represents a new hardware and software architecture that can be used across many Cisco product lines. Cisco offers true consistency in forwarding architecture across product lines in the midrange and high-end routing space.

### 4. MULTIGENERATION

The unique software architecture of the Cisco Processor will allow Cisco to evolve this network processor in the particular time and use the same software across generations of hardware.

Architecture: The Cisco Processor architecture is not in series, parallel processing with centralized shared memory. The processor engine is responsible for all processing of all flows in iterms of running through forwarding-path software, and the traffic manager function is responsible for the input and output interfaces. The task manager converts the packet to other system and vice versa. The Cisco Processor has numerous bandwidth and external references

- This family of network processors supports a range of 5 to more than 100 Gbps of bidirectional external (to the chip) bandwidth across multiple interfaces, and it is destined for actual shared-port-adapter interfaces and the fabric interfaces on distributed systems, as well as traffic to system-specific resources like nroute processor for punted traffic and it is used as both internal and external interfaces.

- The processor's control residing on the host system that integrates the Cisco Quantum Flow Processor is accessed by high speed interfaces. This high-speed interface is used to encode the processor and to distribute tables and databases both to and also from the processor

- Static RAM (SRAM) are used for storing large software libraries, packet buffers, and queuing state.

International Journal of Computer Science and Information Technology Research ISSN 2348-120X (online)

Vol. 3, Issue 3, pp: (155-157), Month: July - September 2015, Available at: www.researchpublish.com

An important aspect of this architecture it can be used in any systems. It will be embedded in the new Cisco ASR 1000. On the Cisco ASR 1000 platform, this chipset is so powerful it will be functioned through the entire forwarding engine of the centralized system

Future scope: the future scope of this paper is to improve the network quality when more number of users are working in a particular service and to avoid that this cisco quantum flow processor is used. For instance, if a result is announced there will be many users will try for the same URL or address. So, there will be a traffic while trying for the particular result.to avoid that these types of network processors are used

# 5. CONCLUSION

By using this cisco quantum flow processor we can able to execute the images, videos and other multimedia relating through network very efficiently.